Providing power to a chip on a PCB (Printed Circuit Board) is no longer a simple task. In the past, ICs were connected to power and ground through fine traces, and these traces did not take much space. As chip speeds increase, they are powered by low-impedance power supplies, such as a power plane on a PCB. Sometimes, only one power plane and one ground plane on a four-layer board are needed to solve most power integrity issues. In addition to the power plane, each IC can also be decoupled to solve the cumbersome power issues in the design.

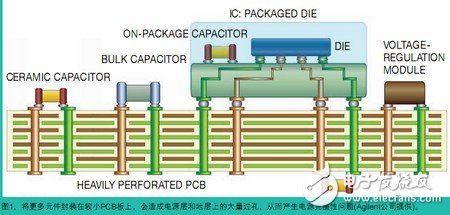

However, the current PCB space (as well as costs and your schedule) is very tight, and these issues also have an impact on the power supply. Dave Kohlmeier, senior director of simulation and simulation products at Mentor Graphics, said: "Consumer and portable devices use less PCB layers for cost savings, but ICs on them require more voltage levels." Not only does it affect portable products, industrial products also have space constraints (Figure 1). The circuitry of a modern cellular base station is housed in a small box on the antenna, and the antenna is usually located in a 19-inch rack inside the building.

Cost is a key factor in high volume consumer products and automotive products. Placing a bunch of potentially unwanted capacitors on the PCB is definitely not acceptable. In order to be successful, the design cycle will be shortened to weeks, rather than years. It is not possible to spend time re-doing PCB boards just to repair and optimize the power and ground layers.

Designing power systems for modern electronics is a daunting challenge. The DDR memory operates at 1600 Mbps and will soon reach 2200 Mbps in quad mode. Worse, it's a single-ended output, meaning that your power system must deal with sudden power supply current challenges. The digital gates in the device may all be on the switch at the same time, the power integrity engineer describes this kind of characteristic as the synchronous switch noise. Serial communications have difficult power requirements. The 802.3ba Ethernet standard requires data rates of 40 Gbps and 100 Gbps (Reference 1).

The operating voltage of modern digital chips is less than 1V, which means that even millivolt noise can cause data-related problems. Multiple chips will increase statistically and cause power drop or overvoltage problems. Your system may be operating for weeks or even months. At the same time, the simultaneous switching of all digital circuits causes the system to restart. These power integrity issues are difficult to detect. The power integrity problem of a single chip in the system may affect other chips in the system, resulting in a reboot. Paul Grohe, a National Analog Devices analog applications engineer, points out: "Even if the nanosecond power loss will make the system unreliable." Steve Patel, product manager of signal integrity at Ansys, said that the key to design reliability is to minimize power. Noise means that digital system engineers must understand the design concepts of analog and even RF.

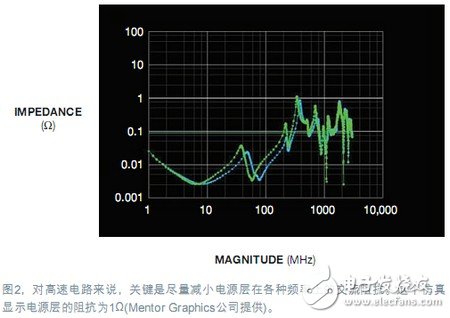

Power system engineers know that the power system must have low impedance (Figure 2), and the concept of the analog engineer is that the noise on the feet of the analog IC power supply is as small as possible. Unlike digital chips, analog chips do not have a noise threshold. The PSRR (Power Rejection Ratio) specification describes how much supply noise will infiltrate the device's output pin. Digital systems engineers must now also deal with the same power noise problem (see sidebar "Please talk to me").

Brad Brim, product marketing manager for Sigrity, said that the power distribution network that supplies power to the chip requires low equivalent inductance: 0.01nH for core voltage and 1nH for I/O power. He pointed out that the power layer couples noise into the signal. In some cases, a signal line placed between two formations has 15mV of noise. When layout personnel deploy the same signal between the power plane and the ground, its noise reaches 45mV.

Power integrity tools can make a decisive optimization of the design. When you do layout optimization, you cannot use an empirical decoupling method. Ansys’s Patel claims that software can help you determine the number, type, and cost of capacitors. These tools can also tell you the effect of changing the distance between layers. For example, Yoshi Fukawa, president and co-founder of TechDream, said that NEC's PI (Power Integrity) Stream can help you by adding or removing capacitors, changing the capacitance and layer shape, and changing the distance between the power layer and the formation. Get your own impedance goals.

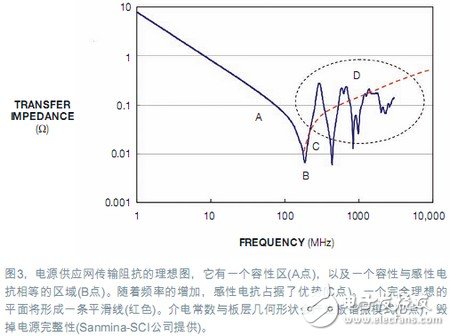

According to Mentor’s Kohlmeier, “You can use CAD files for experiments with what-if analysis. This is much faster than hardware retries. This is the value of virtual prototypes.†Therefore, the use of simulation software is important so that it can be designed. Make critical decisions early in the phase. Changing the location of capacitors, the number of capacitors, and other variables may not affect other departments, but reducing the distance between layers in order to increase the interlayer capacitance affects the entire design team (Figure 3). Sanmina-SCI has a patented modern manufacturing method that can design the interlayer thickness of 4 mil dielectric and increase the capacitance between layers.

way of solving the problem

Kohlmeier said that power integrity simulation is more difficult than expected by many engineers because each capacitor, connection via, and power layer structure must be considered. He pointed out that connecting two levels of vias will reduce the impedance of the supply network, so it is as important as the capacitor. Unlike power integrity, signal integrity generally involves some traces, and the oscilloscope can measure signal integrity in the time domain. Using the Z11 impedance curve from Port 1 to Port 1, simulation of power integrity can obtain frequency domain impedance. To understand the impedance of a power plane, you need a VNA (Vector Network Analyzer), which is difficult to use. Simulation is a complement to measurements, not a replacement, and they provide important information about the performance of the PCB before it is manufactured. Sigrity’s Brim said: “No matter how fast your simulation software is, it's also faster than one measurement.†However, he pointed out that you must have a PCB that you already manufactured to make fast measurements.

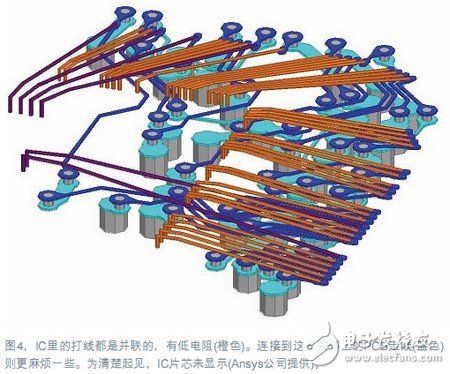

You must believe that the IC designer has done the job and believe that the chip used has no power integrity issues. Ansys’s Patel stated that “the IC and its wires are not the key to power integrity,†because the IC power pins and wires are connected in parallel (Figure 4). Steve Kaufer, director of engineering at Mentor Graphics' HyperLynx, believes that layout engineers who lack the technical know-how to avoid power integrity and signal integrity problems are often the source of the problem.

Power integrity software can help you solve DC and AC problems. In addition, the holes between the power layer and the ground are RF waveguides. To handle the DC problem, it must be ensured that the PCB layer can carry the amount of current that needs to be provided. To deal with communication issues, it must be ensured that the power system can provide the modern chip with the rapidly changing currents required. Finally, note that the waveguide's behavior may be non-intuitive. RF issues are important when dealing with EMI (Electromagnetic Interference) issues, which can make your board incapable of being certified by the FCC (Federal Communications Commission). If a large board surface is used in the design, then it is important to use simulations, and large boards will have resonances. If your board emits RF from the interlayer cavity, proper software simulation can help EMI engineers solve this type of problem. The remedy can be to place the capacitors around the edges of the board. Sun Microsystems, Inc. has a patent 6727780 which uses a resistor in series with a capacitor so that RF energy can be absorbed at the edge of the board and not reflected back into the structure.

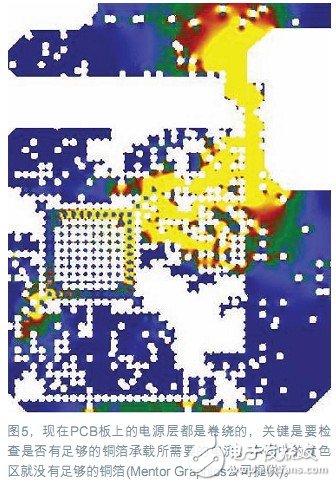

The digital chip requires a large current, which may cause power supply problems of the DC power supply (Reference 2). Both FPGAs and other digital chips require a wide variety of supply voltages, so the power plane must be split to provide multiple voltage rails. The digital chip also has hundreds of pins that require hundreds of vias and cover the copper foil areas of the power and ground layers. It must be ensured that the current density remains below a reasonable value on the copper foil chosen for these layers (Figure 5).

High DC current can also cause thermal problems. The temperature coefficient of copper is 0.4%/°C, that is, the resistance increases by 10% for every 25°C increase in temperature. This increase in resistance occurs under heavy loads, where reliability is critical. The increase in resistance also increases the temperature and reduces the life of components on the circuit board.

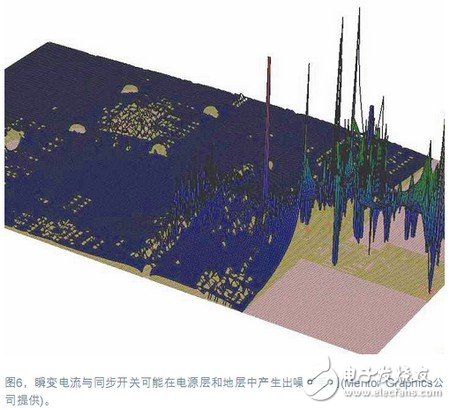

Once there is sufficient copper foil to provide DC loads, attention must be paid to the AC design of the power plane (Figure 6). Power integrity simulation checks the position of the return current through the power plane. In operation, the current intensity obtained by a digital chip is different and varies in nanoseconds. The power supply system must have a sufficiently low AC impedance that can change with current (di/dt, ie, current derivative/time derivative), so that there is no large change in the power supply voltage at the chip pins. Since di/dt also emits electromagnetic energy, these offsets can cause EMI problems. Therefore, signal integrity, power integrity, and EMI compliance are all interrelated. Without simulation, your design may experience crosstalk between holes and other seemingly inexplicable problems.

Software selection

The actual geometry of a power network is very important to its performance, so most software vendors use field solver technology in their power integrity tools (Reference 3).

These tools should give you a quick answer and precise results. RF-IC and system designers typically use a full wave field solver to solve the 3D Maxwell equations. However, the 3D field solver takes a long time to get results, especially for relatively large physical items such as PCB boards. Therefore, power integrity vendors have designed hybrid solver technologies in their power integrity tools. In solving routing, these tools use a 2D solver that uses the fast technology of the transmission line theory. When simulating a plane, the tool can use 2D or 2.5D finite element technology. In some cases, the software can model the vias with a capacitive and inductive model of a lumped-parameter element. For more accurate results, the tool uses a full-wave 3D solver for vias.

In addition, a full-wave solver can also be used to simulate the effects of 3D structures, such as connector pins and other mechanical devices in the power path. Software vendors also put thermal analysis capabilities into their tools. It can be used alone, or it can output heat information to a dedicated thermal analysis tool such as Mentor Graphics' FloTherm, which is a CFD (Computational Fluid Dynamics) 3D simulation environment. Mentor's HyperLynx simulation tool can do its own thermal analysis and output the results to FloTherm, which can build a thermal model of the entire system or a chassis.

Agilent has redeveloped its ADS (Advanced Design System) Momentum product, which provides simulation results for power planes and formations with a large number of vias. It can also be used in designs where the power plane has a small number of traces. MOM (Moment Method) is the fastest simulation method for multi-layer structures. It can solve full 3D fields, including all items in Maxwell's equations. This full-wave scheme takes into account the high-frequency effects of Faraday's law, and Maxwell's substitutional current terms for the Ampère equation (Reference 4). Simulating large layers with MOM is time consuming, so Agilent invented algorithms that reduce the time required to obtain accurate results. Colin Warwick, Agilent’s high-speed digital product owner, said that the tool uses a tree/co-tree approach that can be used to DC.

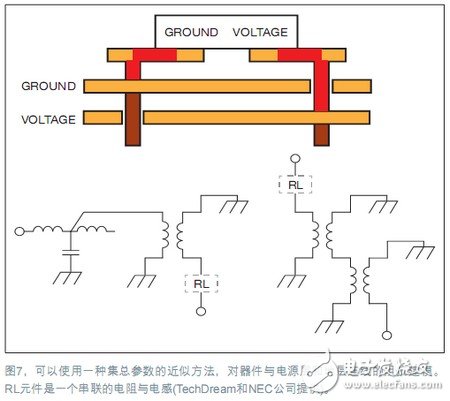

It is also possible to use lumped parameter analysis methods for planar components. NEC's PIStreamn software models planes as a matrix of lumped parameters, making them suitable for analysis using the Spice engine and other lumped parameter techniques. For a plane, the software uses PEEC (Partial Element Equivalent Circuit) technology to generate a RLGC (resistance/inductance/conductance/capacitance) equivalent. The software will also establish a lumped parameter model for the vias and cavities formed between the power plane and the formation (Figure 7). The software also uses a series RLC (Resistance/Inductance/Capacitor) model to model the decoupling capacitor. This model takes into account the parasitic resistance and capacitance of the capacitor and the parasitic resistance and inductance of the fanout traces and vias. You can quickly complete the analysis of a single board pair by creating a simulation run. When changing the settings, the software will make a multi-layer analysis that takes into account all relevant panels.

In addition to simulating the physical structure of the finished board, software tools such as HyperLynx can also perform early floorplanning of board layers and decoupling structures. You can then quickly run an analysis to get some idea about transmission impedance and other variables. Giga Hertz Technologies has developed a faster Spice engine that integrates into NEC's PDN (Power Distribution Network) Expert. With these floorplanners, you can manually outline PCBs and levels and optimize capacitors early in the design process. In this way, the concept of board shape, size, lamination, and number of capacitors can be obtained.

Some of the PC community's power integrity software vendors (such as Mentor Graphics and Cadence) have integrated their tools into the design flow. Although this does not eliminate the concern that one vendor will provide all the tools, power integrity simulation uses a physical representation of the PCB as a geometric model. Both Ansys and Sigrity can accept inputs from Allegro from Cadence, PADS from Mentor Graphics, and company tools such as Zuken and AlTium. Agilent's power integrity tools stem from its expertise in RF design. In addition to its use with ADS design tools, the company's EMPro software can also import PCB data from Allegro from Cadence. Customers often use NEC's PIStream with Zuken's PCB tools, but the software can also accept input data from Cadence's Allegro and other PCB software.

While some engineers prefer their own integration tools in the board flow, obtaining tools from Ansys, a simulation specialist, has some advantages. For example, the company's SI (Signal Integrity) Wave tool is similar to Mentro Graphics' HyperLynx, and the PIAdvisor tool can help you delve into power integrity issues. The tool has a 3D solver for via simulation. In addition, Ansys' HFSS (high-frequency simulator system) tool can be used to perform full 3D simulations of physical problems such as connectors and other 3D geometries. Some customers will output the output of Ansys power integrity tools and signal integrity tools to the same HFSS tool they use to model the chassis. In this way, they can evaluate the EMI of the product. CST (Computer Simulation Technology)'s EM Studio software accepts Gerber PCB file input and can calculate 3D IR (current/resistance) drop.

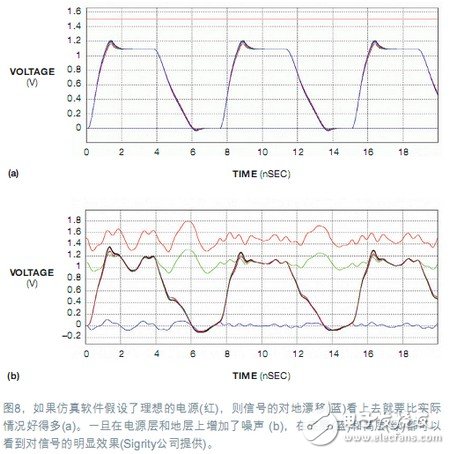

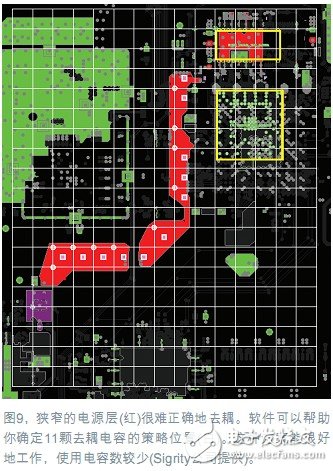

The software you choose must have the capabilities you need. Many companies want you to solve the signal integrity and power integrity issues separately. They assume that once you have fully reduced the power supply impedance, you will focus on signal integrity. The problem with this approach is that power supply noise and signal noise interact. To solve this problem, Sigrity allows you to simulate the effects of power noise on signal integrity (Figure 8). CST's Microwave Studio can also analyze the noise that travels from close proximity to the power plane.

High price problem

The price of power integrity software often stuns inexperienced engineers. A simple DC simulator may cost $15,000, and a complete system with power integrity, signal integrity, and thermal solvers may cost $75,000. This number seems high for software, but it should take into account the cost of power integrity failure. The remake of a complex circuit board may cost $5,000 or $10,000 in production and engineering, while the cost of not being listed in time is $1 million. Another consideration is the BOM (bill of materials) cost of the system. If Power Integrity software can save 50 cents on capacitors, then for a high-volume product, it may be possible to earn back the cost of power integrity software within a few months.

Ansys’ Patel found that the three engineers who used to perform power integrity, signal integrity, and EMI analysis were isolated from each other. Now, although it may still be an engineer doing EMI analysis, the individual must first work with a person who does power integrity and signal integrity analysis. They often share the same software. Sigrity's Brim points out that IBIS

(Input/Output Buffer Specification) 5.0 Power Supply - Ground

The sum signal data allows the simulation software to correlate the noise of the 5.0 model power pin to noise that passes through the output leakage, similar to the PSRR specification in analog devices. All of these functions combine to give you the effect that you have a well-designed, reliable product (Figure 9).

If you understand and know how to use these expensive tools, your identity as an engineer will multiply. For engineers who like CAD (Computer Aided Design) software, the learning of these tools is not difficult. Mentor Graphics offers HyperLynx's free learning courses at many of the company's sales locations. If you have experience with other types of emulators, then learning power integrity tools is basically OK. What needs to be learned and understood is the concept and terminology of the frequency domain, as RF designers do. If you add this knowledge to your existing time domain experience, you will be able to accept the most rigorous design challenges and become a winner.

Data Acquisition Analog To Digital Converters

Shenzhen Kaixuanye Technology Co., Ltd. , https://www.iconlinekxys.com

![<?echo $_SERVER['SERVER_NAME'];?>](/template/twentyseventeen/skin/images/header.jpg)