Whether it's discrete logic, programmable logic, or custom silicon-based digital designs, a stable and reliable clock signal is essential for proper functionality. A poorly designed clock can lead to unpredictable behavior under extreme temperature, voltage, or manufacturing process variations, and can be challenging to debug and expensive to fix. When designing PLD/FPGA systems, several types of clocks are commonly used. These include global clocks, gated clocks, multi-level logic clocks, and wave clocks. A multi-clock system may consist of any combination of these clock types.

1. Global ClockThe global clock, also known as a synchronous clock, is the simplest and most predictable type of clock in a design project. The ideal clocking strategy in PLD/FPGA designs is to use a single master clock driven by a dedicated global clock input pin, which synchronizes all flip-flops in the design. Whenever possible, it's recommended to use a global clock because it offers the shortest clock-to-output delay in the device. This is due to the fact that the global clock pin is directly connected to every register within the PLD/FPGA.

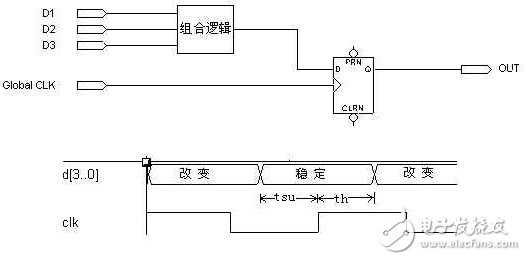

Figure 1 illustrates an example of a global clock. The timing waveform shows that the data inputs D[1..3] of the flip-flop must meet setup and hold time requirements. These values are typically specified in the PLD data sheet and can also be verified using timing analysis tools. If the setup and hold times are not met, the input signal must be synchronized with the clock (see the next chapter on "Asynchronous Inputs").

Figure 1: Global Clock

(It is best practice to use the global clock pin to drive every register in the PLD, ensuring that the data only needs to meet the relative setup time tsu and hold time th.)

2. Gated ClockIn many applications, using a single global clock for the entire design may not be feasible. To address this, PLDs often provide a product term logic array clock, allowing functions to individually clock flip-flops. However, when using such clocks, it's crucial to carefully analyze the logic to avoid glitches.

Gated clocks are typically generated through logic gates. They are commonly found in microprocessor interfaces where address lines control write pulses. Any clock derived from combinational logic is essentially a gated clock. A gated clock can function reliably if the following conditions are met:

- The logic driving the clock should contain only one AND or OR gate. Additional logic can introduce glitches due to race conditions.

- One input to the logic gate acts as the actual clock, while other inputs must be treated as addresses or control signals that adhere to setup and hold time constraints.

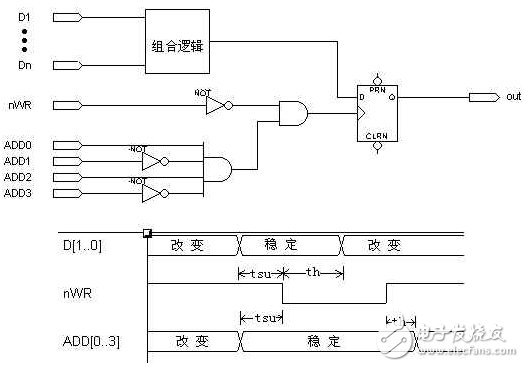

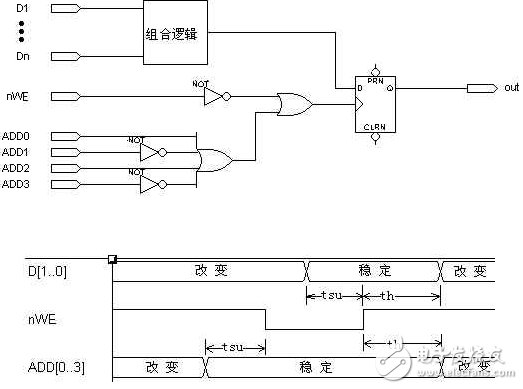

Figures 2 and 3 show examples of reliable gated clocks. In Figure 2, an AND gate is used to generate the clock, while Figure 3 uses an OR gate. In both cases, the nWR and nWE pins act as clock inputs, and the ADD[o..3] pins serve as address lines. The data for the flip-flops comes from random logic based on the D[1..n] signal.

Figure 2: "AND" Gated Clock

Figure 3: "OR" Gated Clock

The waveforms in Figures 2 and 3 illustrate the setup and hold time requirements. The address lines must remain stable during the active period of the clock (nWR and nWE are active low). If they do not, a glitch may appear on the clock, leading to incorrect state changes in the flip-flop. Meanwhile, the data pin D[1..n] only needs to meet standard setup and hold times at the valid edges of nWR and nWE.

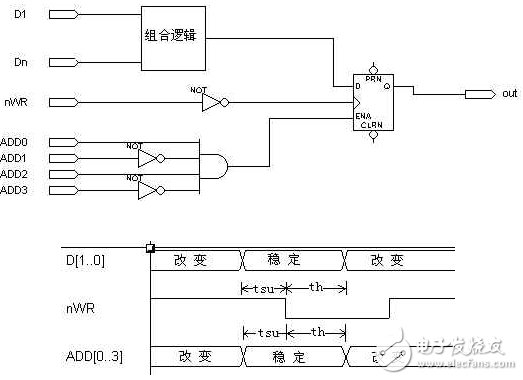

It is often beneficial to convert a gated clock into a global clock to improve reliability. Figure 4 shows how the circuit from Figure 2 can be redesigned using a global clock. Here, the address line controls the enable input of the D flip-flop. Many PLD design tools, like MAX+PLUSII, support this feature. When ENA is high, the D input is latched; when low, the current state is maintained.

Figure 4: "AND" Gated Clock Converted to Global Clock

The timing waveform of the redesigned circuit shows that the address lines no longer need to be stable for the entire duration of nWR being active. Instead, they only need to meet the same setup and hold time constraints as the data pins, reducing the complexity of the address lines.

Figure 5 presents an example of an unreliable gated clock. The RCO output of a 3-bit synchronous counter is used to clock a flip-flop. However, since multiple counter outputs are used as the clock source, it violates the conditions for a reliable gated clock. None of the flip-flops generating the RCO signal can be considered a true clock line, as they all toggle almost simultaneously. Due to potential differences in wiring length between QA, QB, QC, and the D flip-flop, glitches may occur on the RCO line, as shown in the timing waveform of Figure 5.

Servo connectors provides a wide range of metric for small Sensors and actuators.The ingress protection is available and rated to IP 67, these connectors are ideally suited for industrial control networks where small sensors are required. Connectors are either factory TPU over-molded or panel receptacles supplied with sold-cup for wire connecting or with PCB panel solder contacts. Field attachable / mountable Connector is also available for your choice.

Servo Power Cable,M40 Male Power Connector,Custom M40 Power Plug,High Current Power Connector

Kunshan SVL Electric Co.,Ltd , https://www.svlelectric.com

![<?echo $_SERVER['SERVER_NAME'];?>](/template/twentyseventeen/skin/images/header.jpg)